組込ソリューション

回路設計

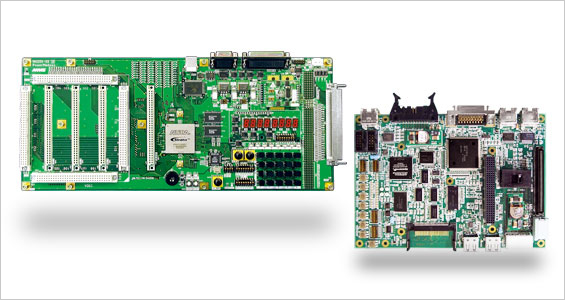

通信機器、レーダー機器等に搭載される高性能のCPUボードおよび周辺ボード開発、アナログボード開発を行っています。

また、機器搭載用のASIC/FPGAの設計も行っています。

ASIC/FPGA設計

- ■特定用途向けシステムLSI(ASIC)設計

- ■画像処理用ASICの回路設計

- ■FPGA設計

エッジAI<FPGA>による画像認識(テクニカルレポート)

物体検知アルゴリズム(Full YOLO Version3)の処理を回路にて実現し小型FPGA(Field Programable Gate Array)デバイスへ実装

深層学習型の人工知能方式は、従来の機械学習と比較して飛躍的に高い検知性能を有しますが、反面、膨大な演算量を必要とし、例えば、一枚の写真の推論に対し約1億種類の係数値との積和演算を実施します。このため、一般のPC(Personal Computer)では処理が仕切れず、高価で消費電力の高いGPU(Graphic Processing Unit)デバイスを搭載したクラウド環境で処理されることが一般的ですが、クラウドでは通信を必要とするため、通信品質や遅延の影響を受けてしまい、用途が限定されてしまいます。端末での AI(Artificial Intelligence)処理を目指す「エッジAI」化のニーズを受けて、2015年頃より世界的に研究開発が進められており、 当社に於いても2019~2021年度にその研究開発を実施しました。

開発技術

- (1) AI処理の特性に適した回路方式【2019年度】

演算量は膨大ですが、同じ処理の繰り返しの多い特性に合わせた小型回路方式の実現に向けて、AI専用プロセッサー回路を開発しました。

また、推論処理は全て回路にて実現しました。 - (2) アルゴリズムレベルでの軽量化【2020年度】

推論精度を維持したうえで、必要な資源(メモリ規模・データ長・処理量等)を抑えるため、独自の学習コントロール技術を開発しました。

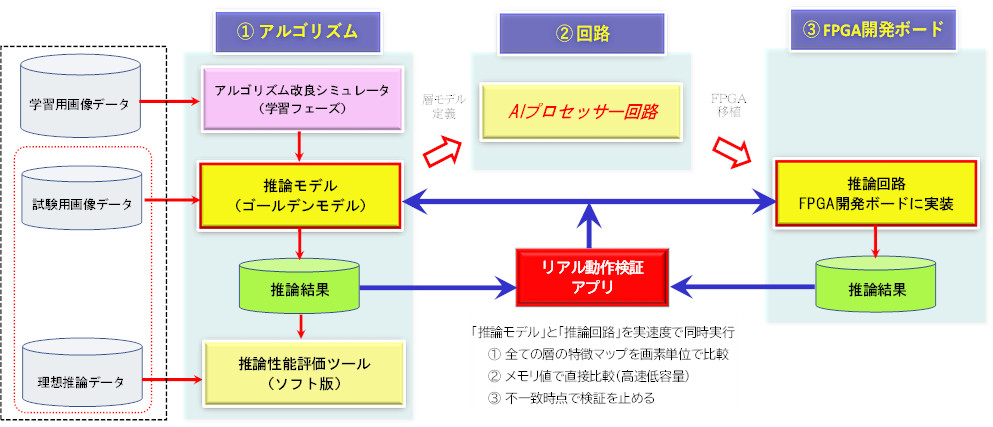

- (3) 既存ツールでは困難な規模の回路検証【2021年度】

HDL-Simulatorでは、1枚の推論動作の回路検証の実行に24時間以上を要しますが、1分以内に実行できる回路検証技術を開発しました。

「リアル動作検証」と命名して国際特許を出願中です。

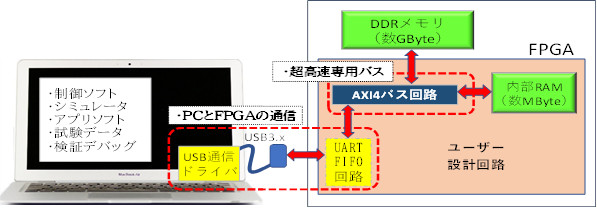

システム構成

開発したシステム構成を示します。ソフトウェアはPython、回路はVerilog-HDLを使用しています。

実装例

Kintex-7 FPGAへの実装事例を示します。

搭載するデバイスが大きくなるに従い、演算並列度を上げることができ、高速処理化が可能となります。

搭載デバイス

| デバイスファミリー [開発キットボード] |

メーカー | レンジ | SoC 有無 |

FPGAスペック | ||||

|---|---|---|---|---|---|---|---|---|

| 周波数 | DDRバス | 回路規模 | 内部RAM | DSP領域※ | ||||

| Kintex-7 XC7K325T [EK-K7-KC705-Gボード] |

Xilinx | ミッドレンジ | 無し | 200MHz | 64bit×1 | 408k reg. | 2.0MB | 乗算器 840個 |

一般概念のDSPプロセッサーでは無く、乗算回路と加算回路を集めた領域。

処理性能

| 処理速度 | 並列処理 | (画素並列×演算並列) | 消費電力 |

|---|---|---|---|

| 4~5fps | 128並列 | (16並列×8並列) | 6.04W |

回路規模

| HDL step数 Verilog-HDL |

LUT as Logic | Register | Block RAM |

|---|---|---|---|

| 16,978 | 172,270 | 168,068 | 340.5 |

電気回路設計

特定用途電気回路/ボード設計

- ■通信機器、レーダー機器用CPUボード設計

- ■通信機器、レーダー機器用周辺ボード設計

- ■各種デジタル/アナログ電気回路設計

ASIC:Application Specific Integrated Circuit(特定用途向け集積回路)の略。半導体集積回路(IC:Integrated Circuit)の分類の一つで、ある特定の機器や用途のために、必要な機能を組み合わせて設計、製造されるカスタムIC。

FPGA:Field Programmable Gate Arrayの略。内部の論理回路の構造を何度も繰り返し再構成できる半導体チップ(PLD:Programmable Logic Device)の一つで、回路規模が数万ゲート以上に及ぶ大規模で複雑な書き換え可能なPLD。

回路設計についてのお問い合わせ

お気軽にお問い合わせ・ご相談ください

電子システム事業統括部

通信機事業所 営業部

受付時間:9時~17時(土日祝祭日および当社休業日を除く)

上のボタンを押すと問い合わせフォームが立ち上がります。ご利用ください。