テクノロジー

技術レポート:アーカイブ

Category:衛星通信システム

FPGAエミュレーションによる組込みS/W のテスト効率化と品質向上

衛星通信システム向け通信機器製品ソフトウェアのテスト効率化と品質向上を実現するため、 FPGA エミュレーターを開発した。

FPGAエミュレーター

は、実際のハードウェアが無い環境でも実機と同等のソフトウェアテストを実施するためのフレームワークである。誤りの早期検出や、実機では実施困難な異常系・準正常系テスト項目の実施が可能となる。

FPGAエミュレーターの特長は、共通部と拡張部(製品固有機能)を明確に分離した構成であり、さまざまな製品への適用を想定している。衛星通信モデムへの適用における改善効果確認をふまえ、今後は、更なる共通化やモジュール化の促進によっ

て、より効率的に 使えるテストフレームワークに改良していく予定である。

参考情報:

- この技術レポートは、当社が展開する宇宙・通信事業の衛星通信システムソリューションに係る技術について著述されたものです。

- 衛星通信システムソリューションは、通信機事業所が提供しています。

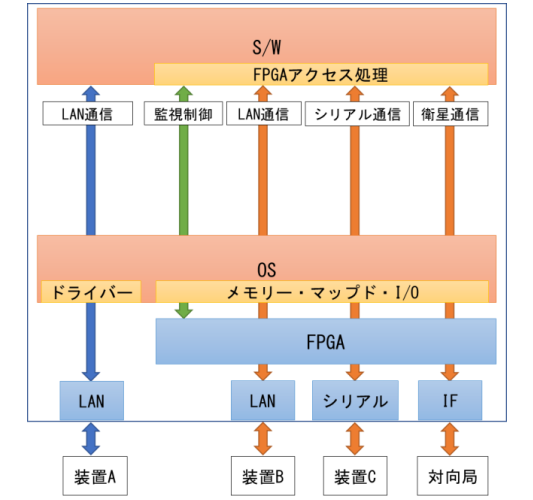

FPGA エミュレーションによる組込みS/W のテスト効率化と品質向上 1FPGA エミュレーションによる組込みS/W のテスト効率化と品質向上三原 拓也,佐藤 亨,徳田 伸矢1. まえがき筆者の所属する部門では,衛星通信システム向け通信機器製品(モデム,衛星ルータ,等)のソフトウエア(以下,S/W)を設計・製作している。本稿では,衛星通信モデムS/W 向けのテスト環境としてFPGA エミュレーターを開発した取組みについて報告する。(FPGA:Field ProgrammableGate Array)FPGA エミュレーターの適用により,衛星通信モデムS/Wのテスト効率化と品質向上を実現した。また,S/W とハードウエア(以下,H/W)の並行開発が可能になり,製品全体の工期短縮にもつながった。本稿では,S/W のテストフェーズの呼称を,表1 のとおり定義して使用する。表1.テストフェーズ呼称■結合テストモジュール全体を組み合わせたS/W を,製品実機のH/W とは異なる環境(例:PC 上の仮想環境)でテストする。H/W の構成要素(筐体,FPGA,DSP など)や周辺機器は,S/W シミュレーター等で模擬する。■総合テストモジュール全体を組み合わせたS/W を,製品実機(実機相当)のH/W 上でテストする。FPGA 等も実物を使用する。周辺機器は,基本的には模擬とするが,実機を使用する場合もある。 2. 組込みS/W 開発の課題2.1 S/W・H/W 構成とS/W テスト典型的な衛星通信モデムについて,S/W・H/W の構成図を図1 に示す。衛星通信モデムの特徴として,S/W は,メモリー・マップド・I/O を介して,FPGA のレジスターにアクセスする。FPGA は, S/W からの要求に従い,モデムH/W 自身の監視制御に加え,周辺機器(図1 の装置B,装置C)との通信や,衛星回線経由で対向局(図1 の対向局)とのデータ送受信を中継する役割を担う。そのため,FPGA が無い環境で行う結合テストでは,FPGA とのインターフェースのみならず,周辺機器や対向局との通信も,そのままではテス図1.衛星通信モデム構成図トすることができない。その場合の主な対応は,以下のものである。総合テストで実施する(結合テストでの実施をあきらめる)FPGA へのアクセスを模擬する仕組みを構築する次節以降で,それぞれの対応について詳しく述べる。2.1.1 総合テストで実施する場合FPGA へのアクセスや,FPGA 経由で実現する通信機能のテストについて,結合テストでの実施をあきらめ,総合テストで実施するとした場合,コスト超過や工程遅延のリスクが発生する問題がある。S/W の開発フェーズの下流にいくほど,不具合が発生した際の上流フェーズへの手戻り作業が多くなるため,不具合1 件あたりの改修コストは高くなる。FPGA 関連のテストを,総合テストで初めて実施した場合,本来は結合テストで検出するはずであった誤りを総合テストで検出することになり,工数・コストが計画から増加してしまう可能性がある。加えて,テストでFPGA 関連のインターフェースに齟齬が検出されると,不具合が解決するまでの期間,他のテスト項目が実施できない場合が多い。その場合,テスト再開FPGA エミュレーションによる組込みS/W のテスト効率化と品質向上2までに時間を要し,コスト超過や工程遅延となる。また,昨今の衛星通信モデム製品の開発においては,S/WとH/W が並行で開発されることが多く,H/W 製造工程の影響をS/W が受けやすい。仮に,総合テストを開始するタイミングでH/W がまだ完成していない状況が発生すると,総合テストが開始できず,S/W の工期にも遅延が発生する。2.1.2 FPGA へのアクセスを模擬する場合衛星通信モデムS/W の開発において,結合テストはPC上の仮想環境で実施している。結合テスト環境としての理想は,S/W のインターフェース機能や全体のシーケンス動作を確認するための,周辺機器,及び自装置のH/W が揃っていることである。特に,実機では発生させにくいH/W の異常やクロスシーケンスなどを狙って発生させ,テストすることができれば,S/W 品質の向上につながる。図1 に示した構成において,S/W と直接ネットワーク経由でつながる周辺機器(装置A)に関しては,シミュレーターをホストPC 上で動作させることで,比較的容易にインターフェース機能をテスト可能である。一方,図1 においてFPGA 経由で通信を行う周辺機器(装置B,装置C)や対向局については,FPGA が無い環境では,そのままではテストが実施できない。FPGA エミュレーター導入以前の衛星モデム製品では,S/W のソースコードにテスト用のスタブを記述し,結合テスト時には,S/W のうちFPGA とのインターフェースを行う機能をコンパイルオプション等でスタブに切り替えることでテストを実施していた。スタブは,特に共通化設計されておらず,実施したいテスト内容に合わせて製品ごとに機能を作り込んでいた。このような従来手法には,以下のような問題があった。周辺機器との間のさまざまなシーケンスをテストするためには,テスト項目ごとに決められた動作をするスタブを作成する必要があり,効率が悪い。テスト用コード自体のテストを実施しないため,誤りを含むスタブでテストを実施してしまう可能性がある。スタブに置き替えた部分のS/W は,結合テストで動作を確認することができない。結果として,結合テストでは検出できない誤りや,実施できないテストが発生し,2.1.1 項と同様の問題が発生していた。3. FPGA エミュレーター3.1 構成2 章で述べた課題を解決するため,FPGA エミュレーターを開発した。FPGA エミュレーターを使用した構成を,図2に示す。FPGA エミュレーターは,S/W の結合テスト環境にて,S/W から見たFPGA 及びその先にある周辺機器や対向局との連接をテストするための仕組み(フレームワーク)とし,S/W と同じOS 上で動作するミドルウエアとして実現した。FPGA エミュレーター適用のため,図2 左側に示すように,FPGA にアクセスする部分のS/W 機能をFPGA アクセスライブラリーとして切り出した構成とした。図2.FPGA エミュレーターを使用した構成図FPGA エミュレーションによる組込みS/W のテスト効率化と品質向上3結合テストにおいては,図2 右側のように,FPGAアクセスライブラリーを,FPGA エミュレーター用に差し替える。これにより,S/W 本体を改修することなく,製品実機環境とFPGA エミュレーター環境を容易に切替え可能となった。3.2 機能3.2.1 S/W テスト向け機能開発したFPGA エミュレーターの機能ブロック図を図3 に示す。図3.FPGA エミュレーターの機能ブロック図FPGA エミュレーターは,さまざまな製品向けに活用できるよう,SPL(Software Product Line)の考え方をもとにアーキテクチャー設計を行った。製品に依存せず完全流用が可能な部分(共通部)と,製品ごとに動作が変わるため作り込みが必要な可変部分(拡張部)を明確に分けることで,各製品の開発者がFPGA エミュレーターを採用しやすい構成とした。FPGA エミュレーターの主な機能を表2 に示す。表2. FPGA エミュレーターの主な機能■周辺機器連接機能S/W から見て,FPGA を経由した先にLAN やシリアルで接続される周辺機器(実機又は,シミュレーター)を接続できる。■衛星回線・対向局連接機能S/W から見て,FPGA を経由した衛星回線の送受信をLAN で模擬し,さらにその向こうにある対向局についても,周辺機器と同様にシミュレーターとして接続できる。■FPGA レジスター模擬機能S/W からのFPGA レジスターアクセス(Read/Write)に対し,それぞれ個別にフック(選択)処理を記述でき,レジスター間の連携や,条件処理も実現できる。■S/W 割込み模擬機能衛星モデムにおいては,FPGA からS/W への通知手段として,S/W 割込みが使用される。S/Wは専用のドライバーを介して割込みを検出している。FPGA エミュレーターは,ドライバーの差替えにより,任意のタイミングでS/W 割込みを模擬できる。■LED 模擬機能モデム筐体の各種LED(例:電源ON/OFF,キャリアON/OFF,異常発生有無,等)の点灯/消灯を任意のレジスターのビットに割り付け,画面上に模擬表示できる。■動作ログ出力機能レジスターのアクセスや周辺機器との通信内容など,動作ログを詳細に出力可能。テストの結果確認やエビデンス記録として使用できる。3.2.2 FPGA エミュレーター自体の自動テストFPGA エミュレーターを製品に適用する際には,拡張部をそれぞれの製品S/W に合わせて作り込む必要があるが,この部分の品質が悪いと,2.1.2 で述べたような問題が発生する。その対策として,この作り込み部分を含め,FPGA エミュレーター自体のテストを容易に実施するための自動テスト機能を,FPGA エミュレーターに具備した。自動テストの構成を図4に示す。FPGA エミュレーションによる組込みS/W のテスト効率化と品質向上4図4.FPGA エミュレーターの自動テスト構成図4. 製品への適用4.1 衛星通信モデムS/W衛星通信システム向けモデム装置のS/W 開発において,結合テストにFPGA エミュレーターを適用した。適用時の構成を図5 に示す。図の中央,"拡張部"の部分だけが,モデムS/W 向けにFPGA エミュレーターに新たに追加した機能である。その実装には,図5.衛星モデム適用時の構成図FPGA エミュレーター自身の自動テスト機能を活用した。これにより,テスト環境自体の品質確保を効率よく実現することができた。例えば,FPGA エミュレーターに仕様変更が発生し改修を行う場合でも,改修部分以外への影響が無いことを自動テストで確認できるため,デグレードの発生を未然に防ぎ,品質を確保することができた。4.2 改善効果結合テストにFPGA エミュレーターを適用した衛星モデムS/W について,結合テストと総合テストにおける検出誤り数の割合(計画値/実績値)を図6 に示す。図6.検出誤り数の割合(計画値/実績値)なお,検出誤り数の割合は,結合テストの計画値を基準(100%)とした割合で示している。計画値は,過去の類似製品の実績値と,衛星モデムS/W のS/W規模から見積もった値であり,FPGA エミュレーターを適用しなかった場合の予測値である。図6 の結合テスト実績値の緑色部分は,総合テストで検出する見込みであった誤りを,結合テストで早期検出したものである。また,早期検出した誤りのうち,約62%は,FPGA 経由で連接する周辺機器とのインターフェース誤りであった。FPGA エミュレーター適用の効果が,狙いどおりに実現できている。2.1.1 項で述べたとおり,結合テストと総合テストとでは,検出した誤り1 件あたりの調査・改修コストが違ってくる。FPGA エミュレーターの活用により,誤りを上流の結合テストで検出することで,テストの効率化が実現できた。また,2.1.2 項で述べた,実機では発生が難しい異常系・準正常系のテストについても,特別な仕組み等を追加することなく容易にテスト実施できる環境により,効果的なテストを従来よりも多く実施するFPGA エミュレーションによる組込みS/W のテスト効率化と品質向上5ことで,S/W 品質の向上につなげることができた。一方,FPGA の厳密な動作タイミングや性能についてのテストは,FPGA エミュレーターを用いた結合テストでは実施できず,実機でのテストが必要である。結合テストと総合テストで,それぞれどのようなテスト項目を実施するのがテスト全体の効率化につながるのか,更なる分析を進め,改善に取り組んでいる。5. むすび衛星通信システム向け通信機器S/W のテストに関する課題に対し,FPGA エミュレーション技術の適用による改善効果を確認した。FPGA エミュレーターは,衛星通信モデムのシリーズ製品の他,衛星ルータ製品,衛星以外の無線通信モデム機器など,さまざまな製品に適用範囲を広げており,実績を重ねている。今後は,各製品で作成したFPGA エミュレーターのノウハウを活かし,更なる共通化や,拡張機能のモジュール化の促進によって,より効率的に使えるテストフレームワークに改良していく予定である。謝 辞FPGA エミュレーターの実現・製品適用にあたり,ご指導賜った三菱電機(株)通信機製作所 ソフトウェア技術部 ソフトウェア技術第二課の皆様に,深く感謝の意を表する。執 筆 者 紹 介三原 拓也(みはら たくや)2014 年入社。衛星・通信に関する組込みソフトウエア開発に従事。現在,第1事業部 電子通信技術部 技術第4グループに所属。佐藤 亨(さとう とおる)2003 年入社。衛星・通信に関する組込みソフトウエア開発に従事。現在,第1事業部 電子通信技術部に所属。徳田 伸矢(とくだ しんや)2014 年入社。衛星・通信に関する組込みソフトウエア開発に従事。現在,第1事業部 電子通信技術部 技術第4グループに所属。