テクノロジー

技術レポート:アーカイブ

Category:FAソフトウェア開発

マイクロシーケンサCPUユニット FX5UJのH/W開発

三菱電機は、マイクロシーケンサ「MELSEC iQ-Fシリーズ」のラインアップ拡充として、制御規模256点以下の小規模装置向けCPUユニット「FX5UJ」を開発した。FX5UJは、上位機種のFX5Uと同等の基本性能を持ちつつコストパフォーマンスに優れた機種である。入出力点数24点、40点、60点の3タイプを揃え、近年の工期短縮や保守容易化の要求実現のため、同一価格帯の従来機種ではオプションのEthernetポート、SD(Secure Digital)カードスロットを標準で搭載する等、充実した外部接続用インタフェースと豊富な内蔵機能を備えている。当社は、FX5UJのH/W開発に携わり、上位機種のFX5Uに続き、FX5UJでも重要部位である制御基板とインタフェース基板の開発を担当した。本稿では、FX5UJの概要と、FX5UJのH/W開発において、当社が担当した制御基板の開発時に発生した課題とその対策について述べる。

参考情報:

- この技術レポートは、当社が展開するFA・産業メカトロニクス事業のFAソフトウェア開発ソリューションに係る技術について著述されたものです。

- FAソフトウェア開発ソリューションは、名古屋事業所が提供しています。

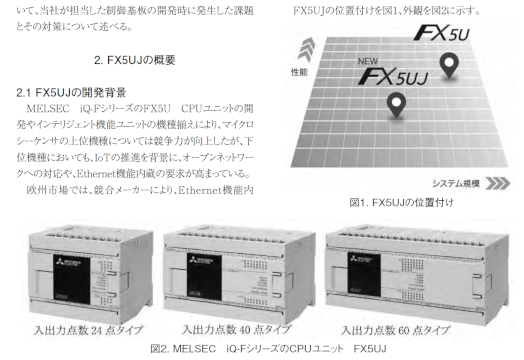

マイクロシーケンサCPUユニット FX5UJのH/W開発 1. まえがき 三菱電機は、マイクロシーケンサ「MELSEC iQ-Fシリーズ」のラインアップ拡充として、制御規模256点以下の小規模装置向けCPUユニット「FX5UJ」を開発した。FX5UJは、上位機種のFX5Uと同等の基本性能を持ちつつコストパフォーマンスに優れた機種である。入出力点数24点、40点、60点の3タイプを揃え、近年の工期短縮や保守容易化の要求実現のため、同一価格帯の従来機種ではオプションのEthernetポート、SD(Secure Digital)カードスロットを標準で搭載する等、充実した外部接続用インタフェースと豊富な内蔵機能を備えている。当社は、FX5UJのH/W開発に携わり、上位機種のFX5Uに続き、FX5UJでも重要部位である制御基板とインタフェース基板の開発を担当した。本稿では、FX5UJの概要と、FX5UJのH/W開発において、当社が担当した制御基板の開発時に発生した課題とその対策について述べる。 2. FX5UJの概要 2.1 FX5UJの開発背景MELSEC iQ-FシリーズのFX5U CPUユニットの開発やインテリジェント機能ユニットの機種揃えにより、マイクロシーケンサの上位機種については競争力が向上したが、下位機種においても、IoTの推進を背景に、オープンネットワークへの対応や、Ethernet機能内蔵の要求が高まっている。欧州市場では、競合メーカーにより、Ethernet機能内蔵、SDカードスロットを内蔵し、ネットワーク機能、ストレージ機能を強化した下位機種のCPUユニットが展開されている。また、中国市場でも、競合メーカーにより、Ethernet標準搭載の下位機種が展開されている。更に国内市場では、競合メーカーの下位機種が、三菱電機マイクロシーケンサの上位機種FX5Uと下位機種(旧モデル)間の価格帯で市場展開されており、競合するケースが増加している。このような中、旧モデルの下位機種は、価格的には競合他社と大きく変わらないが、EthernetやSDカードスロットを搭載することで、競争力を向上する必要があった。三菱電機では、マイクロシーケンサの下位機種やiQ-Fシリーズ全体の競争力強化を図るため、iQ-Fシリーズとして、EthernetポートやSDカードスロットを搭載し、コントローラ間通信やCC-Link IE フィールドネットワークBasic対応による周辺機器、FA機器との接続性を強化した「MELSECiQ-Fシリーズ FX5UJ CPUユニット」を開発した。FX5UJの位置付けを図1、外観を図2に示す。図1. FX5UJの位置付けマイクロシーケンサCPUユニット FX5UJのH/W開発名古屋事業所 技術部 FA開発第2課射延 誠悟図2. MELSEC iQ-FシリーズのCPUユニット FX5UJ40マイクロシーケンサCPUユニット FX5UJのH/W開発一般論文2.2 FX5UJのH/W開発コンセプトFX5UJは、旧モデルの下位機種に対してEthernetポート、SDカードスロットを標準で搭載し、基本機能を上位機種のFX5Uと同等にすることが求められた。そのため、Ethernetポート、SDカードスロットを標準搭載するFX5Uの設計資産を活用しつつ、必要機能をコンパクトなサイズで実現することと、積極的にV E( V a l u eEngineering)を推進して低コスト化を図ることが、H/W開発のコンセプトになった。図3にFX5UJの基板構成を示す。図3. FX5UJ基板構成具体的な開発の目標を以下に示す。2.2.1 小型化の目標FX5UJのサイズは、旧モデルの下位機種に対して、更に小型化を実現することが目標に設定された。小型化のポイントは、旧モデルでオプションだったコネクタ変換器を、FX5UJは内蔵した構造とした上で、旧モデルのCPUユニットにコネクタ変換器を装着した寸法に対して、FX5UJのCPUユニット単体の寸法を小さくすることである。コネクタ変換器は、Ethernet通信アダプタやアナログ入出力機能アダプタなどの、特殊機能を持ったアダプタを旧モデルのCPUユニットに接続する際に用いる。旧モデル開発当時の技術では、コネクタ変換器を内蔵するとCPUユニットの寸法が大きくなり、コストも増加するため、コネクタ変換器をオプションとし、CPUユニット単体の小型化と低コスト化を前面に出す方針が採用された。最新の技術と工夫により、FX5UJへのコネクタ変換器の内蔵を実現することができれば、旧モデルに対する小型化と低コスト化に寄与することができる。特に、Ethernet通信においては、旧モデルがコネクタ変換器とEthernet通信アダプタを必要とすることに対して、FX5UJの場合はコネクタ変換器の内蔵に加えて、Ethernetポートを内蔵するため、旧モデルに対する小型化と低コスト化に対する効果が最も大きい。また、SDカードスロットについては、旧モデルの場合はオプションでも装着が不可能であった。FX5UJはSDカードスロットを内蔵しつつ、旧モデル以下のサイズを目標にした。具体的な目標値を図4に示す。図4. FX5UJ外形寸法の目標41マイクロシーケンサCPUユニット FX5UJのH/W開発2.2.2 低コスト化の目標マイクロシーケンサの下位機種における収益性を向上するため、FX5UJは上位機種FX5Uに対してコストを改善することが目標に設定された。目標達成に向けて、FX5UJの構成要素である基板、構造部品、加工費ごとに目標コストを割り付けて、VE活動を推進することになった。当社は制御基板とインタフェース基板のVE活動を担当した。3. 小型化の取組み小型化の実現に向けて、以下の方針を定めて取組んだ。①部品の小型化②部品配置の最適化による高密度設計以下に各項目の取組み詳細を示す。3.1 部品の小型化(1) 各回路ブロック共通部品の小型化以下の各回路ブロック共通部品の小型化を図った。①チップ抵抗アレイの採用②コンデンサのダウンサイジング③ロジックICのダウンサイジング④基板間コネクタ付近のバイパスコンデンサ削減(2) Ethernet周辺回路の小型化1パッケージ部品のパルストランスを、ディスクリート部品の回路で構成することにより、小型化を図った。(3) 基板間コネクタの小型化制御基板とインタフェース基板を接続するコネクタの小型化のために、FX5UJ専用品を新たに開発した。(4) 拡張ボード・アダプタ制御回路の見直し以下の回路見直しにより、バッファICを3個から1個に削減した。①アダプタの2台目とボードのデータ通信信号の共用化②バッファ挿入する信号線を20本から8本に削減(5) リセット回路の小型化FX5Uではマニュアルリセット機能を周辺回路で構築していたが、FX5UJはマニュアルリセット機能を内蔵したリセットICを採用し、周辺回路を削減した。(6) 時計機能回路の小型化時計機能回路については、時計用クロック内蔵ICの採用による周辺回路の削減を図った。また、時計用クロック内蔵ICに低消費電力タイプを選定したことにより、バックアップ用電気二重層コンデンサの小型化を図った。3.2 部品配置の最適化による高密度設計高密度化による配線幅の不足や配線間の間隔不足による信号品質の低下を軽減するために、部品配置の最適化に取組んだ。FX5UJにおいては、MCRが設計を担当したFX5Uの制御基板の部品配置、配線長をもとに、上流工程で三菱電機と連携して各信号線の配線条件を検討した。本稿では、最も高密度化が要求されるCPU周辺回路の配線条件について述べる。3.2.1 各部品の配線長条件C P Uから、A S I C( A p p l i c a t i o n S p e c i f i c Integrated Circuit)(注1)、SDRAM、FLASH ROM、LED制御ICへの配線は、信号の伝搬遅延時間のバラツキや反射等の影響が出ないよう、図5に示すように、最大配線長(α)、各デバイス間最大距離(β)、最大分岐長(β/2)を定義し、可能な限り短く配線する。また、実装面積削減やクロストークノイズ防止などの観点より、最小配線幅と最小配線間隔(γ)、隣接信号配線との平行配線長の条件を表1のように定義した。図5. 各部品の配線長条件表1. 最小配線幅と最小配線間隔、 隣接信号配線との並行配線長(注1 ) 電子部品の種別の1つで、特定の用途向けに複数の回路を1つにまとめた集積回路。42マイクロシーケンサCPUユニット FX5UJのH/W開発3.2.2 各信号における配線条件以降に、各信号における配線条件を示す。(1) クロック信号(図6)① クロック信号はエッジを使用するため、他の信号の影響を受けないように、両側にシールドパターンを配置する。② シールドパターンの両端は必ずビアホールに接続し、シールドパターンが長くなる場合は、許容間隔以内(図中δ以内)でGND層とビアホールを介して接続する。ビアホールはバイパスコンデンサなどのビアホールと共有しないこと。③ 可能な限り内層で配線する。図6. クロック信号の配線条件(2) データ信号、アドレス信号、制御信号(チップセレクト信号など)(図7)① 主線(β)と分岐配線(β/2)は全体を最短で配線し、主線と分岐配線の線長バランスは分岐配線を最短とする。② SDRAM の制御信号線において、プルアップするチップセレクト信号は、最短で配線する。③ 信号線同士の間隔及び他の信号線との間隔は、最小配線間隔(γ)以上確保する。図7. データ信号の配線条件3.3 小型化の取組み成果取組みの結果、2.1.1項で述べた小型化の目標値を達成した。4. VEの取組みVEの取組みでは、回路設計・部品選定の方針を以下のとおり定めた。(1) 制御回路(CPU・メモリなど)F/W資産の活用による流用率向上のため、FX5Uと同等のCPUとメモリのスペックが必要であり、FX5Uから流用する。(2) インタフェース回路(Ethernet、SDカード、USBなど)F/W資産の活用による流用効率向上のため、FX5Uと同等のスペックが必要であり、FX5Uから流用する。ただし、USBはFX5U非搭載のため、新規設計する。(3) iQ-Fシリーズ共通部品接続される増設ユニット、拡張アダプタ等は共通であるため共通部品(バスASIC、拡張コネクタ)・回路を、FX5Uから流用する。(4) 電子部品選定新規メーカー含めて選定候補とし複数社の購買競合によるVEを積極的に推進するため、新規に選定する。また、将来の中国生産時の現地調達も考慮してメーカー選定を行う。これらの設計方針に基づき、以下の①②をテーマにして、制御回路・インタフェース回路設計段階のVEに取組んだ。①製品に対する材料費比率の高い回路のVE②代替部品の積極採用によるVE以下に各項目の取組み詳細について述べる。4.1 材料費比率の高い回路のVE基板単体のコスト低減を実現するため、以下に取組んだ。(1) 基板配線の最適化による制御基板層数削減FX5Uの制御基板の層数は6層であり、FX5UJクラスの回路ボリュームにおいても、従来は6層が標準的な仕様であった。FX5UJは低コスト化を追求するために、4層への削減に取組んだ。従来は、内層のうち2層を電源専用として配線し、信号は別の層に配線していたが、FX5UJは電源と信号を同一層に配線し、層数削減を実現した。層数削減により、基板単体のコストを35%低減した。43マイクロシーケンサCPUユニット FX5UJのH/W開発(2) 制御基板共用化による適用数量拡大従来は入出力点数ごとに制御基板を開発していたが、FX5UJでは40点タイプと60点タイプの制御基板共用化に取組んだ。40点タイプのサイズ内に60点タイプの回路を収めるため、3章で述べた高密度設計を採用した。40点タイプと60点タイプでは、入出力状態表示用LEDの数量が異なるが、実装パッドを60点タイプに合わせて設計し、40点タイプで使用する場合はLEDを非実装にすることにより、共用化を実現した。適用数量の拡大により、基板単体のコストを6%低減した。4.2 代替部品の積極採用によるVE代替部品の積極採用については、コストフォロー表を作成し、基本仕様書会議から試作図面会議までの間、三菱電機と共同でコストフォロー会議を実施した。コストフォロー会議では、約730種類の部品、1点1点に対して活動進捗を確認し、目標コスト達成までの進捗の見える化を図り、未達成や遅れている活動について解決案を協議するなど、活動の促進を行った。代替部品の積極採用による、主な部品のVE成果を表2に示す。表2. 代替部品のVE成果4.3 VEの取組み成果制御基板・インタフェース基板におけるVE活動の結果、コスト目標を達成することができた。5. 発生課題と改善取組みFX5UJの制御基板は実装面積が厳しく、ノイズ源と部品間の間隔不足、電源配線幅の縮小の影響により、耐電圧・ノイズ耐量において仕様を満足できない箇所があった。以下に該当箇所と改善の取組みを示す。5.1 耐電圧性能向上の取組み24点タイプ制御基板の一次試作品において、Ethernet通信用のコネクタ信号端子と増設ケーブル間、コネクタシェルと増設ケーブル間、コネクタ信号端子とコネクタシェル間の耐電圧が、判定値を満足しなかった。原因は、Ethernet通信用のコネクタシェルと信号配線間の間隔不足と、コネクタシェルとパルストランス絶縁後のGND間の間隔不足であった。なお、Ethernet用パルストランスは、単体で耐電圧の判定値を満足することが確認できたため、部品単体には原因がないことを確認した。以下に対策を述べる。(1) コネクタシェルと信号配線間の間隔不足対策対策前の耐電圧は判定値の80%であった。したがって、最短間隔箇所の距離を1.25倍以上に拡大することで判定値を満足すると推定し、配線変更を実施した。上記の配線変更によるEthernet伝送路特性について、事前にANSYS SIwaveを活用したシミュレーションにより、対策前後の特性に変化がないことを確認した。(2) コネクタシェルとパルストランス絶縁後のGND間の間隔不足対策(1)と同様に、最短間隔箇所の距離を拡大した。Ethernet伝送路特性の影響についても、(1)同様に問題ないことを確認した。(3) 対策効果の確認結果上記(1)(2)の配線変更後の耐電圧を、24点タイプ制御基板の二次試作品において実機確認し、判定値を満足した。また、40点/60点タイプ制御基板の設計段階で本対策を反映し、一次試作品において耐電圧を満足できることを確認した。5.2 ノイズ耐量性能向上の取組み24点タイプの一次試作品において、Electrical FastTransient/Burst試験を実施した。ノイズ印加箇所がAC電源の条件時に、SDカードへの書込み又は読出しが正常完了しない現象が発生した。原因は、電源基板のAC端子から発生する輻射ノイズによる影響であった。以下に原因詳細と対策を述べる。(1) 原因SDカードスロットはインタフェース基板に実装している。インタフェース基板と電源基板のAC端子は、小型化実現の制約上、クリアランスが小さいため、設計段階でSDカードスロットへの輻射ノイズの影響が懸念された。44マイクロシーケンサCPUユニット FX5UJのH/W開発したがって、インタフェース基板は、電源基板のAC端子に面する側の輻射ノイズ伝搬経路になり得る領域を、予め配線禁止領域と定めて配線設計した。配線イメージを図8に示す。この設計により、インタフェース基板と電源基板のAC端子のクリアランスを確保したが、輻射ノイズの遮蔽効果が低下し、透過した輻射ノイズの影響を受ける弊害が生じた。(2) 輻射ノイズの透過防止対策インタフェース基板は実装面積の制約が厳しく、SDカードスロットを電源基板のAC端子から離すことは極めて困難である。したがって、インタフェース基板の層数を2層から4層に変更して、増やした層をGND層に割り当て、遮蔽板とすることを検討した。層数増加に伴うコストアップの影響は、ほぼ無視できるレベルであり、本対策を採用した。対策内容を図9に示す。図9. 輻射ノイズの透過防止対策(3) 対策効果の確認結果上記(2)の配線変更後のノイズ耐量を、24点タイプの二次試作品、40点/60点タイプの一次試作品において実機確認し、判定値を満足した。6. むすび本稿では、マイクロシーケンサMELSEC iQ-FシリーズのCPUユニットであるFX5UJのH/W開発における制御基板の開発について紹介した。FX5UJの開発では、過去の設計資産を活用し、要求された小型化と低コスト化を実現できた。FX5UJはEthernetを搭載することにより、多種多様なネットワーク上のパソコンや機器との接続が可能になった。また、SDカードスロットの搭載により、ネットワーク上のパソコンや機器からの情報を定期的にSDカードに保存し、保存されたデータの活用による装置の稼働状況やトラブル原因の解析を効率よく行うことができるようになった。今後も、今回培ったノウハウを継承するとともに、最新技術やユーザーの要望を収集・検討し、マイクロシーケンサMELSECシリーズの開発を進めていく。最後に、本開発及び執筆に当たり、様々な面で支援いただいた社内外の関係者の方々に深く感謝を申し上げる。執筆者紹介射延 誠悟 イノベ セイゴ1989年入社。主にシーケンサMELSECシリーズ製品のハードウェア開発に従事。現在、名古屋事業所技術部FA開発第2課課長。図8. インタフェース基板一次試作品の配線イメージ45マイクロシーケンサCPUユニット FX5UJのH/W開発